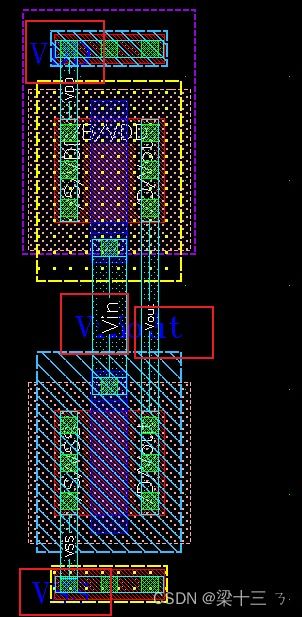

从0开始学习Cadence Virtuoso 反相器Layout设计与后仿真

三、反相器Layout设计与后仿真

1. Layout设计基础

在完成反相器的电路原理图设计后,我们需要进行Layout(版图)设计,这是集成电路物理实现的关键步骤。

Layout设计准备工作:

- 确保电路原理图已经通过DRC检查

- 确定工艺文件(PDK)已正确加载

- 熟悉工艺设计规则

- 了解器件尺寸和连接关系

2. 反相器Layout绘制步骤

a) 创建Layout视图

在Library Manager中,为反相器cell创建Layout视图,进入Virtuoso Layout Editor界面。

b) NMOS和PMOS器件放置

- 使用Create->Instance放置NMOS和PMOS晶体管

- 注意PMOS需要放置在N阱中

- 根据原理图尺寸设置晶体管的W/L参数

- 确保器件间距满足设计规则

c) 金属连线

- 使用Metal1层连接源极和漏极

- 输入信号连接到两个栅极

- 输出信号从漏极连接点引出

- 电源VDD使用Metal1连接到PMOS源极

- 地线VSS使用Metal1连接到NMOS源极

d) 接触孔和通孔

- 在需要连接的不同层之间添加接触孔(Contact)

- 多晶硅与金属1之间需要添加相应的接触孔

3. DRC检查

完成Layout绘制后,必须进行DRC(设计规则检查):

`

Verify->DRC

选择相应的工艺规则文件

运行检查并修正所有违规

重点关注:

- 最小间距

- 最小宽度

- 包围规则

- 天线效应`

4. LVS验证

LVS(版图与原理图对比)确保Layout与原理图一致:

Verify->LVS

设置原理图和版图源

运行对比

检查器件匹配、网络匹配

修正不匹配项直到完全通过5. 寄生参数提取

在通过DRC和LVS后,进行寄生参数提取:

Verify->Extract

生成带有寄生参数的网表

提取电阻、电容等寄生元件6. 后仿真设置

a) 创建后仿真配置

- 在ADE L界面创建新的仿真配置

- 选择提取的寄生参数网表

- 设置与原理图仿真相同的激励和参数

b) 后仿真分析`

瞬态分析:观察输入输出波形

直流分析:检查电压传输特性

交流分析:分析频率响应

Monte Carlo分析:考虑工艺偏差`

7. 前后仿真对比

关键性能指标对比:

- 传输延迟时间

- 上升/下降时间

- 功耗

- 噪声容限

- 驱动能力

常见差异分析:

- 寄生电容导致的延迟增加

- 寄生电阻引起的电压降

- 耦合效应带来的信号完整性问题

8. 优化与迭代

根据后仿真结果进行Layout优化:

- 调整器件尺寸

- 优化布线拓扑

- 减少寄生参数

- 改善匹配特性

9. 经验总结

- Layout规划很重要:在开始绘制前做好整体布局规划

- 对称性设计:保持电路对称以获得更好的匹配特性

- 电源完整性:确保电源和地线有足够的宽度

- 信号完整性:关键信号线应尽量短且直

- 多次验证:DRC、LVS必须完全通过才能进行后仿真

通过反相器的Layout设计和后仿真,我们建立了完整的集成电路设计流程,为更复杂电路的设计打下了坚实基础。在实际项目中,这个过程需要反复迭代,直到所有性能指标都满足设计要求。

如若转载,请注明出处:http://www.mykmlife.com/product/10.html

更新时间:2026-04-27 12:44:12